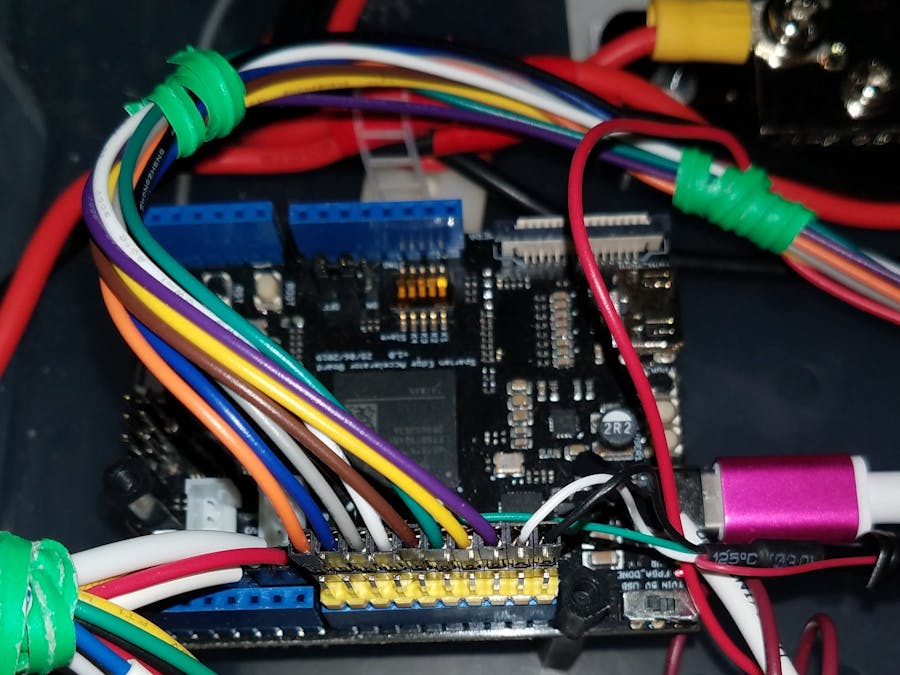

Last year (2020 during the Covid lockdown) I purchased a SEEED Studio Spartan Edge Accelerator platform intending to up my skills in XILINX FPGA development with XILINX toolchains. I knew there was support for direct based Arduino development through an add-on SEEEDuino board or it could be programmed with a simple JTAG programmer.

I wanted to do industrial/aerospace control project prototyping using XILINX toolchains and needed a "barebones" FPGA platform for what I wanted to do in my lab, so I chose to avoid using the Arduino environment and focus on barebones/baremetal FPGA programming (disclaimer: I have no argument with Arduino fans, and I wanted to do RTL-Verilog, RTL-VHDL and HLS-C++/C mixed development).

This is part 1 (August 2021) of a series and I will be updating this write up as I include additional parts. For easy reference, here are the articles in planning.

Aug 2021 | Xilinx Vivado board files for Spartan Edge Accelerator - 1

TBD 2021 | Xilinx Vivado board files for Spartan Edge Accelerator - 2

TBD 2021 | Spartan Edge Accelerator - Simple Heartbeat RTL

TBD 2021 | Spartan Edge Accelerator - Digilent PMOD OLEDRGB display

TBD 2022 | Spartan Edge Accelerator - Digilent PMOD OLEDRGB/ KYPD control displayOne good thing about using the XILINX Spartan platform for development is that any project developed for this platform would be able to be reused in more complex FPGA parts (e.g., on the Zynq PS/PL platforms, such as Avnet's Minized, which I am also developing on in tandem with this platform).

The Spartan Edge Accelerator (SEA) platformIn inspecting the board I found that the onboard XILINX Spartan-7 FPGA and peripherals (you can read about them from the technical documentation available through various snippets and links found at the product's website mentioned at the top of this project) and the schematics/PCB of the platform showed there were plenty of devices present that could be used in a great number of realistic/useful FPGA projects and if designed carefully could be integrated to control other complex system of systems. I also spent some time to look at the number of pins available for various projects (I plan to write up future projects using Digilent PMOD modules and this platform) assuming that some of those pins were directly attached to the FPGA device and not to the other peripherals or other chips. I would like to acknowledge the skills of SEEED Studio hardware designers and give them compliments as they provided Eagle Schematic and PCB layouts with the technical documentation for reference (and hey, I don't think they will mind if we copy their work with attribution), like that I am embeddeding below. This is from the schematics/PCB zip file as viewed in a licensed copy of Autodesk Eagle.

I won't go into the details of all of the components in this project writeup, and what I think can be done, but will if I get time in the future post projects that I have got running using Digilent PMOD modules, XILINX toolchain (Vivado/Vitis) and my custom board files. Of course, if anyone has developed a complete board file for all the on-board peripherals, please consider sharing, the board is compact enough, and cheap enough to be used in any number of designs in my opinion and comes with various power supply and interface options!

At the present time for this first project writeup (Part 1) I present version 2.42X of my files. As I improve them, I will increment the version number of the file package, so later (higher) numbers should mean more features.

If you feel the files are useful in your development efforts, please share your experiences and drop me a line, or suggestions as you think fit.Developing XILINX Vivado board files

I noticed early on in my introduction to Vivado that they required (for any "supported" FPGA board, custom or otherwise) a set of board files to be present, and presented as fully validated and checked files that would be in a fully specified board repository location, for any FPGA board containing parts/peripherals. Without diving into the details of what needs to be included in the board files per XILINX document UG895 (for those adventurers, see Appendix A: Board File and related sections) I started with clones of other vendor's board files and made sure to test sections manually while looking for hints on how the syntax had to be presented. At present, the files I am attaching here work with the instructions/guide enumerated in Vivado Design Suite User Guide System-Level Design Entry UG895 (v2020.2) February 12, 2021. I can't guarantee they will continue to work with older versions, but for 2019.x and 2020.x, they do work for me.

Instructions

- Download the attached X2.42 zipped folder (updated 10/26/21 - you will find this folder in the Custom Parts section as X2.42 Zipped Folder) to any convenient directory on your computer, ensuring it is placed as close as you can to the topmost hard drive folder of your drives. This is to avoid situations where the total length of the entire folder and its files exceeds the file name limitations of your operating system. (And we are still looking at you XILINX-AMD (ex: https://support.xilinx.com/s/question/0D52E00006iHsmE/windows-path-name-length-problem?language=en_US is a common complaint) for a 21st century solution to long path name handling by XILINX codebase, and support for spaces in file names.

- Expand the zipped folder, you will find a simple directory with three files. Refer to UG895 for details, but generally it should look like:

03/05/2021 04:18 PM 34,744 board.xml

03/05/2021 03:41 PM 9,764 part0_pins.xml

06/01/2020 09:18 PM 19,945 preset.xml

05/07/2020 12:56 AM 166,902 Spartan-Edge-Accelerater-Board-v1.0-wiki.jpg

Place all four files in the same folder and all together as specified including the JPEG picture file. The file entries interact with each other. - Close all instances of Vivado/Vitis, etc. This step is important. The Vivado startup scripts scan the folders you have defined for all necessary files, and thus we have to define it first in Vivado, then we have to close Vivado, and then start Vivado once again.

- Note:If the steps below don't work for you, or you can't find the proper board files after this, something has happened to the syntax of the board files during your copy/transfer, or the location you specified is invalid, and thus you will have to look into the matter, or ask questions - Check the TCL log files! I am open to questions but depending upon my workload may not be able to answer in time, and ask that you try to debug yourself first.

- Startup Vivado (tested: 2019.x, 2020.x) as normal. Look for menu options such as Tools > Settings and in Settings > Tool Settings > XHub Store > Board Repository (or similar) add in an entry for a board repository path to the directory that you have created when you unzipped the folder mentioned above. Press OK to record the setting and then completely exit out of the Vivado program for now.

- Now you have to take steps to install the Digilent PMOD IP directory, and a short guide is to use their github directory and clone it to your local computer. Then specify that as an additional directory in Settings > Tool Settings > IP Defaults > IP Catalog > Default IP Repository Search Paths.

- Startup Vivado once again, and choose File > Project > New (or equivalent) and proceed to create a Vivado project. Choose to create a RTL Project or other project, it shouldn't matter, but be careful when you have to choose a part.

- This is where you have to select Boards (or equivalent) and at this stage, Vivado will attempt to load all boards it can find (from default, from specified Board Repository locations) and if all is well (I have struggled here many times) you will see a list of vendors to show up.

- Select seeedstudio.com from the vendor list and it should show the following entry:

- Now select that board definition in any part of that entry which is white in color, otherwise you will be taken to the website of the product, and press NEXT > FINISH.

- At this stage you are dropped into the main Vivado screen where you can quickly create a new block diagram and pull the following components from the board file which are already tagged with the most appropriate preset IP modules I could find. If you have loaded the PMOD libraries as specified above, and if all goes well, this process now gives you access in the Vivado RTL environment for the following Schematic signals:

SYSCLK (100 MHz)

FPGA_RST (inverted!)

BUTTONS x2

LED x2

Programmable LED x2

12-bit single ch. D/A converter U6 DAC7311IDCKR (work in progress)

8-bit A/D converter (ADC_IN pin ext conn (work in progress)

PMOD JA connector

SOFT UART TXD/RXD

I2C Bus (work in progress)Once you have success in generating a validated block diagram, you can proceed with Synthesis > Bitstream generation and the output will be constrained due to FPGApins already defined (constrained) per the board files. If you don't like them, you should be given a chance to change the pin-outs, but the definitions work for me (for example, a pseudo JA port is mapped to available pins that are open, for example) and a list is provided below for your convenience. I am sure some of the entries have mistakes as I am testing, and would appreciate if anyone would point out errors in the list.

Logical Map > Pin Map > FPGA Port MapSee attached code files (ascii, plain text)

Comments