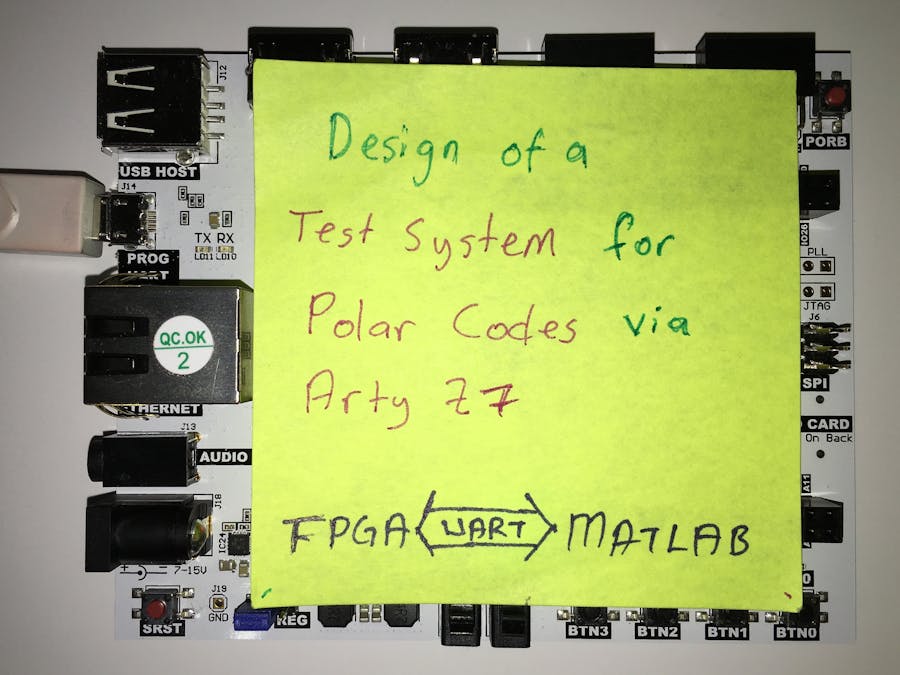

Polar codes are a channel coding technology which is most probably used in near future's trend 5G networks. Communication links are susceptible to errors due to random noise, interference, etc. That errors corrupt the original message at the receiver. Channel coding basically employs a set of algorithmic operations on the original data stream at the transmitter, and another set of operations on the received data stream at the receiver to correct these errors. In this project, a test system for polar codes will be implemented on Arty Z7 FPGA card using VHDL. We want to make our system very flexible. Flexible means that users can change any varible like message bits count, coding rate, binary erasure channel error probabilty whenever they want. So that, we need to send commands to FPGA and receive outputs from FPGA. Due to less amount of leds, switches on Arty Z7 board we decided to use serial communications like UART. We implemented and tested UART receiver and transmitter. For commands, we decided to create own operating codes table. In UART, message bits counts are eight, so first 4 bits are operation and last 4 bits are relevant data for selected operation. You can see first version of operation codes in Fig1, that table will be improved during development time.

We successfully implemented Polar Encoder and tested. Polar encoding is XOR operation according to some rules. It can be done static XORs for static message lengths but due to our flexibility mission, we use G_Matrix method for encoding operation. Each 1 (one) in the G_Matrix shows XOR operation. You can see that G_Matrix for eight bits and relevant XOR scheme in Fig2.

And in Fig3, here is the simulation result of our Polar Encoder implementation. In our implementation G_Matrix calculated from scratch according to 8 bits. We checked the encoded data Erdal Arıkan who is the inventor of the Polar Codes and it is true.

We used Nexus 3 for testing UART because it has 8 leds and switches. You can see UART receiver in Video 1 also UART transmitter in Video 2.

To sum up, we implemented UART receiver, transmitter and Polar Encoder. We not implement UART operation codes because we focus on the Polar Decoder and most probably we will finish Polar Decoder in ten days. After the completion of FPGA parts we start the benchmark runs using operation commands and receive results of the benchmark runs. As the outcome of the project, we will create bit error rate(BER) graphs using received results from FPGA and we will see how close polar codes proposed for todays popular technologies like 5G networks will achieve a bit rate performance of Shannon’s theoretical limit. In video 3, you can watch short presentation about our project.

Thanks for reading so far.

Comments