Field Programmable Gate Array vs FPGA is an programmable dispositive that contains logic blocks with configurable conexion.

A big advantage to use an FPGA is parallel programing and execute, not sequential like microcontrollers.

VHDLA language for FPGA developed by IEEE that's very different to Verilog, but personally VHDL is easier than verilog.

How to ProgramThe program is simple.

First download the Mojo Base program in the official page.

https://github.com/embmicro/mojo-base-project/archive/master.zip

This Mojo Base program has this docs.

All modules was program using Verilog, we don't never modified the branch "avr_interface."

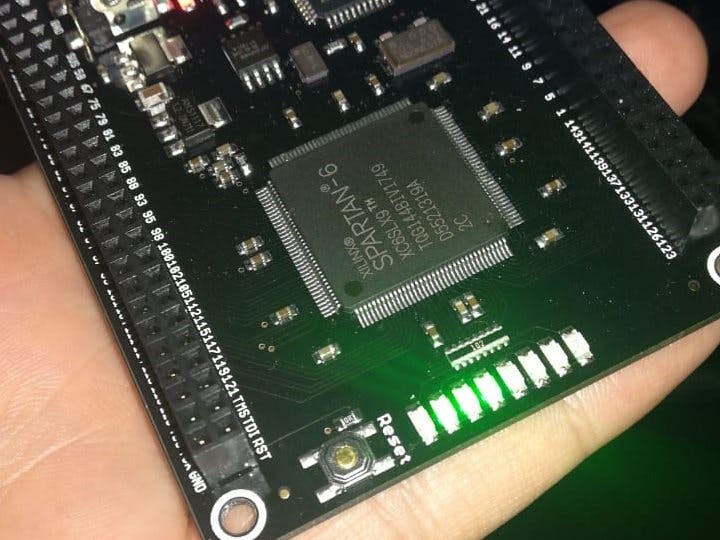

Now double clic on "xc6slx9-2tqg144" and select in "Preferred language" the option "VHDL" and click "OK."

Now right click on "xc6slx9-2tqg144" and select "New Source...".

Select VHDL Module, write a File name and Next.

The wizard have a tool for the signals declaration but I not use that, so click on next and finish.

The base program for the mojo use all built it led, so copy the ucf file in the new VHDL module this should look like this (you also can add a new ucf file and copy the content).

After delete the branch "mojo_top".

Now we work in the file "mojobincount" this module has 3 parts.

The Libraries Declarations:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

The Physical Signal Declarations:

entity mojobincount is

Port ( clk,rst_n : in STD_LOGIC;

led : out STD_LOGIC_VECTOR (7 downto 0);

cclk,spi_ss,spi_mosi,spi_sck,avr_tx,avr_rx_busy : in STD_LOGIC;

avr_rx : out STD_LOGIC :='0';

spi_miso: out STD_LOGIC :='0';

spi_channel : out STD_LOGIC_VECTOR (3 downto 0):=B"0000");

end mojobincount;

In this part is need to declare some signals implicit for the Mojo V3 like "cclk, spi [...]"

We really only use these signals

- clk

- rst_n

- led (this is a vector of 8 values)

architecture Behavioral of mojobincount is

signal contador : STD_LOGIC_VECTOR (26 downto 0) :=B"000000000000000000000000000"; --Hex 50M=2FAF080

signal leds : STD_LOGIC_VECTOR (7 downto 0) :=B"00000000";

begin

process(clk,rst)

begin

if rst = '0' then

led<="00000000";

elsif rising_edge(clk) then

contador <= contador+1;

if(contador>=x"2FAF080")then

leds<=leds+1;

led<=leds;

contador<="000000000000000000000000000";

end if;

if(leds>="11111111")then

leds<="00000000";

end if;

end if;

end process;

end Behavioral;

In the begin of the process we declared some "virtual" signals, a counter of 27 values and another counter of 8 values called "leds".

The clock of Mojo V3 is 50Mhz it's means each 50 Million of pulses are a Second, use the counter of 27 values for "count" each rising edge of the clock then compare this with the Hex value for 50 Million ("2FAF080") then add 1 to "leds" and assessing this value to the physical output "led".

Finally throw back the counter to 0 and throw back the led to 0 if this is in the max value ("11111111").

The UCF FileThe ucf file relates all physical pins of the FPGA to the port declarations in our program

NET "clk" LOC = P70 | IOSTANDARD = LVTTL; #For single

#For vectors

NET "led<0>" LOC = P134 | IOSTANDARD = LVTTL;

NET "led<1>" LOC = P133 | IOSTANDARD = LVTTL;

NET "led<2>" LOC = P132 | IOSTANDARD = LVTTL;

NET "led<3>" LOC = P131 | IOSTANDARD = LVTTL;

NET "led<4>" LOC = P127 | IOSTANDARD = LVTTL;

NET "led<5>" LOC = P126 | IOSTANDARD = LVTTL;

NET "led<6>" LOC = P124 | IOSTANDARD = LVTTL;

NET "led<7>" LOC = P123 | IOSTANDARD = LVTTL;

Now save all and click on this option.

If all it's ok this should look like this.

Then click on "Generate Programming File" this option begin the process for Synthesis and implement design for finally create the bin file located in the "syn" directory.

This have some warnings, but no errors.

Mojo has a Loader in the official page, after install all drivers the loader only select the serial port of the FPGA, find the bin file in the "syn" directory, clic on "Erase" and then clic on "Load"

Ta daaa, that's all.

Comments