FTDI FT2232H Fast serial interface uses the following 4 pins:

- FSDI, input, data, receive serial data

- FSCLK, input, clock in serial data from FSDI and FSDO

- FSDO, output, serial data out from FT2232H

- FSCTS, output, driven low to indicate the FT2232H us ready to send data

Detailed timing diagrams are in the data sheet in section 4.8.1 of the FTD223H chip.

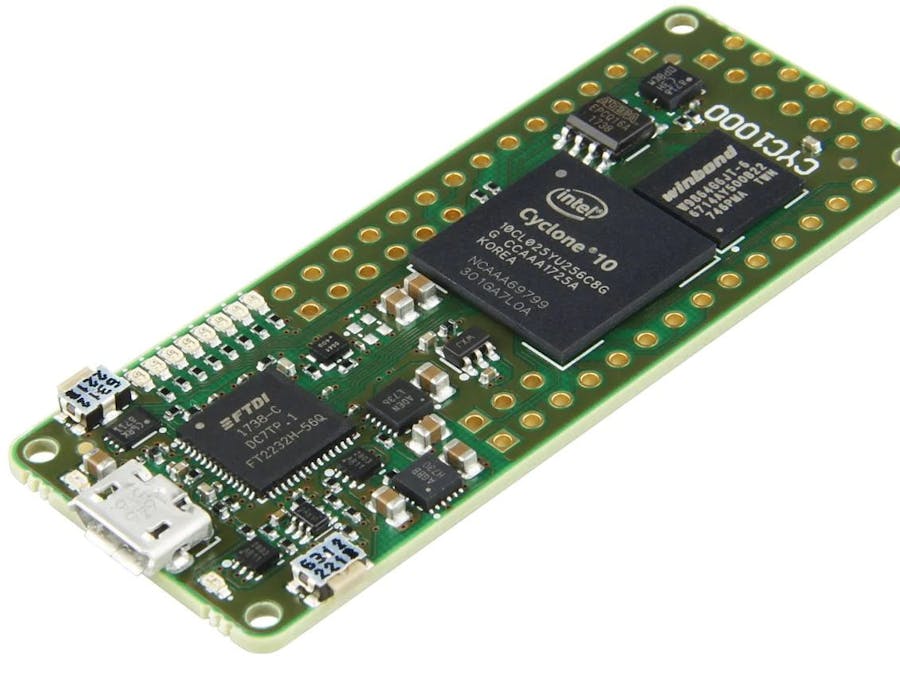

CYC1000 FPGA pin out to the FT2232HThe Cyclone 10LP FPGA on the CYC1000, is connected to the FT2232H chip using the following pins:

- FSDI is connected to pin R7

- FSCLK connected to pin T7

- FSDO connected to pin M8

- FSCTS is connected to pin M8.

To enable the Fast Serial mode need to change Port B to use OPTO Isolate, attached is a screen shot of the change using FTDI programmer.

Now, the CYC1000 serial interface will be using Fast Serial hardware handshaking instead of standard two pin serial. For the PC side, using Linux Ubuntu 18.04, there is no need to load any drivers, the interface can be accessed via ttyUSBx.

Quartus Lite 18.1Load the fast serial project, from the menu File-> Open project -> fast_serial.qpf

From the menu select tools-> platform designer->select avalon_fast_serial.qsys

After loading the platform designer file the Avalon Bus will be displayed.

Here is a description of each block:

- Master is the Avalon bus master that communicates to each slave.

- in_bytes_to_packets: takes the bytes from the Fast Serial rx_module.v module into a stream to forward the the Master

- out_bytes_to_packets: takes the stream from the Master and converts to a bytes stream for Fast Serial tx_module.v

- led_gpio_slave: is an Avalon Memory mapped slave to the Master. The address is 0x0 to 0x3F.

- sysid_qsys_0: Is an Avalon Memory mapped slave to the Master. There are two registers, System ID, hard coded to 0x112233. and Time Stamp.

There are 3 basic modules to Fast Serial,

- clock_fastserial.v: divides the clk by 2.

- rx_fastserial.v: Uses FSDO and FSCLK pins of the FT2232H to create byte interface for the Avalon bytes to stream interface.

- tx_fastserial.v: FSCTS, FSDI and FSCLCK pins to create a byte interface packet to byte stream interface to transmit bytes back to the PC

Section 43 Avalon -St to Packets and Packets to Bytes Converter Cores describes the byte stream.

Here is a basic description, the packets use an encoded byte stream, so any bytes that are reserved get encoded with an escape sequence. The frame has a SOP, start of packet 0x7A, EOP end of packet 0x7B and a channel 0x7B. This is taken from the manual:

If the endofpacket signal on the core's source interface is asserted, the core inserts an end of packet (0x7b) before the last byte of data.

If the channel signal on the core’s source interface changes to a new value within a packet, the core inserts a channel number indicator (0x7c) followed by the new channel number.

If a data byte is a special character, the core inserts an escape (0x7d) followed by the data XORed with 0x20.Loading the FPGA

From the menu select Tools -> Programmer the following dialog should appear. Use the start button to load the image into the FPGA RAM.

Python Example

In the python directory is an example application to get the FPGA ID and toggle the LEDs. Need to have serial_asyncio installed.

At the console: python3 avalon_loopback_serial.py

The LEDs should increment.

Increase performance of ttysetserial /dev/ttyUSBx low_latency

x the USB device the CYC1000 is connected, for example, mine is /dev/ttyUSB0 so the command would be:

setserial /dev/ttyUSB0 low_latency

This uses a lower timer latency timer in the FT2232H to increase draining the FIFOs. Since the commands are less then 512bytes (min USB packet size for High Speed USB) the timer will expire to send the data. The timer can be set to 0, so every micro-frame the data is sent.

Increase the performance even more, use libftdi1 and C, I'm still working getting the performance a little better, and addressing several bugs, but was able to achieve ~180us round-trip.

Comments