Though now the machine learning acceleration flow on MPSoC devices are gone to Vitis-AI flow, the DNNDK flow might be followed less. However we are releasing the DNNDK flow based DPU (3.0) TRD for Ultra96 V1 FPGA.

We are also releasing the Vitis-AI based tutorials soon!

In this tutorial we have used the DPU (3.0) IP with DPU architecture= 1152. This architecutre consume less resources (LUT, BRAM and DSP). And we dont have the channel argumentation, softmax etc, which is shown here:

The initial design and configuration is taken from the DPU integration tutorial, we migrated that project to VIVADO 2019.1. We updated the DPU IP (3.0) and setup the IP configuration again. Now synthesis done, then we use this Tcl command before implementation:

set_param place.runPartPlacer 0Without this Tcl command you might get timing error on the project. After implemented, create Bitstream of the project and then export it (including bitstream). Now after the process will involve on Petalinux 2019.1.

Petalinux DevelopmentThe Petalinux steps are also listed here:

- Steps included here: xilinx-Resnet50_on_Ultra96v1_2019_2.pdf

- Petalinux steps explained here to: dpu-3-0-trd-for-zcu106

Reference Link: https://forums.xilinx.com/t5/AI-and-Vitis-AI/resnet50-sample-app-error-on-ZCU104/td-p/1045798

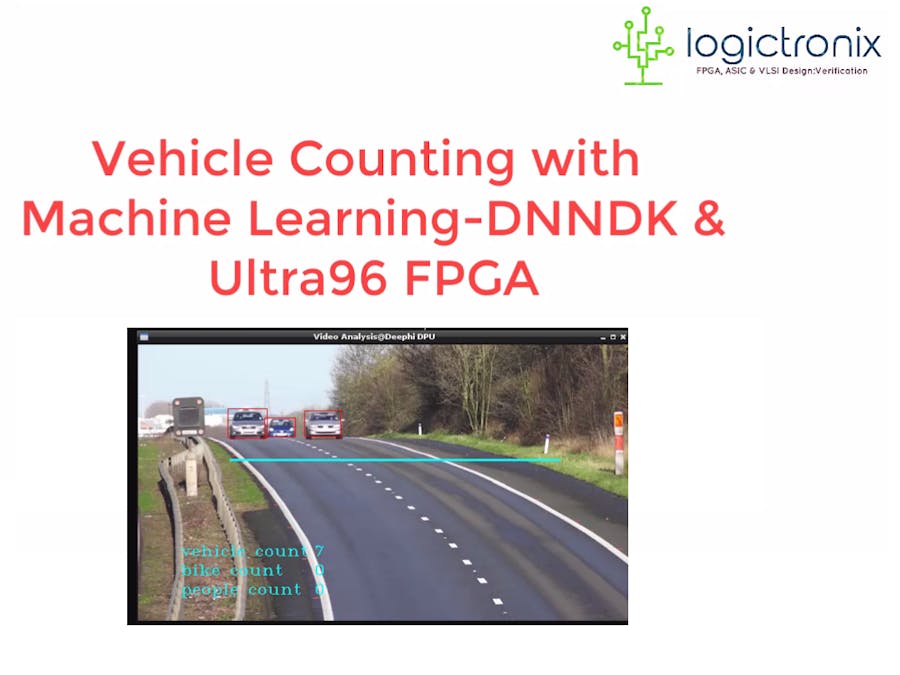

Some of recent Development on ML Acceleration with DPU on Ultra96 from LogicTronix are:- Social Distancing detection/measuring and alarming solution

- Vehicle Counting Application for Traffic Analysis

For these ML applications and more, please write us at: info@logictronix.com

Thank you for going through this tutorial!

![LogicTronix [FPGA Design + Machine Learning Company]](https://hackster.imgix.net/uploads/attachments/1123066/_SyVIfEqFUU.blob?auto=compress%2Cformat&w=40&h=40&fit=min&dpr=2)

![LogicTronix [FPGA Design + Machine Learning Company]](https://hackster.imgix.net/uploads/attachments/1123066/_SyVIfEqFUU.blob?auto=compress%2Cformat&w=60&h=60&fit=min&dpr=2)

Comments