In this project, we have many aims. Like accomplishing a data compression (source coding) algorithm in VHDL, wireless communication in between two FPGAs. Using ASK modulation in wireless transmission. Additionally, reducing storage and saving time and using less bandwidth while the image is transmitted.

INTRODUCTIONIn the transmitter part, an image will be saved inside creating Block Read-Only Memory of transmitter FPGA, and this image is shown on a monitor via using VGA port. After that this image is eliminated from redundant bits and the data size reduces 8 bits to 3 bits. It is based on by determining RGB.

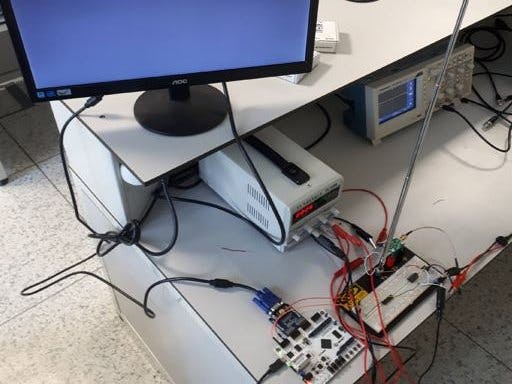

First image size was 32x48 and the data number of it was 1536 bits for testing quickly. We also used Nexys 3 boards and ISE Design Suite 14.2 program in first. Nexys 3 board consist of more LED's and switches to see and test the design clearly. At the receiver part, data was sent by wireless communication with ASK modulation. The received data is saved in the block RAM. The next step is to display the received data on the screen via the 2nd FPGA. During the second test cycle, we adapted the whole system into the Arty A7 boards and Vivado 2017.4. Besides in the second step we used 10800 data bits which is our original data number of images and the image size is 120x90.

II. METHODSII.I. Image CompressionDevelopment application of multimedia, there is growing need to store and process large sizes of digital images but enhancing in hardware for capturing and demonstrating digital images, also the size of this image increases. Moreover, image compression techniques are developed because of these needs. In this project we interested in data redundancy process which is eliminating unwanted bits. Data redundancy is the first step of the image compression. By eliminating unwanted bits, we transmit image data quickly and easily.

Coding RedundancyUsually in a digital image the number of bits used for the representation of each pixel is constant for all the pixels, regardless the value of the pixel and the frequency of occurrence of that value in the image. By variable length coding the average number of bits used per pixel in the image is decreased and thus the reduction the redundant code.

Compression is useful because it reduces resources required to store and transmit data. The advantages of using data compression are obvious absolutely. Redundancy makes time shorter, storing less space and transferring less time and less bandwidth.

II.II. VGA ProtocolVGA is a standard interface for controlling analog monitors. The calculating side of the interface provides the monitor with horizontal and vertical sync signals, color magnitudes, and ground references.

The horizontal and vertical sync signals are 0V/5V digital waveforms that synchronize the signal timing with the monitor. Being digital, they are provided directly by the FPGA (3.3V meets the minimum threshold for a logical high, so 3.3V can be used instead of 5V).

The color magnitudes are 0V-0.7V analog signals sent over the R, G, and B wires.

A video controller circuit must be designed in the FPGA to drive the sync and color signals with the accurate timing for produce a working display system.

Horizontal sync (HS) and vertical sync (VS) timings signals are generated by VGA and coordinating the delivery of video data based on the pixel clock. The pixel clock explains the time available to show one pixel of information. The VS signal explains the “refresh” frequency of the display, or the frequency at which all information on the show is rework. The number of lines to be demonstrated at a given refresh frequency defines the horizontal “retrace” frequency.

Horizontal-sync counter driven by the pixel clock to generate HS signal timings. It can be used this counter to locate any pixel location on a given row. Likewise, the output of a vertical-sync counter that increments with each HS pulse can be used to generate VS signal timings, and it can be used this counter to locate any given row. These two continually running counters can be used to form an address into video RAM. No time relationship between the onset of the HS pulse and the onset of the VS pulse is specified, so it can be arranged the counters to easily form video RAM addresses, or to minimize decoding logic for sync pulse generation.

II.III. Amplitude Shift Keying (ASK) or Pulse Amplitude Modulation (PAM)

Amplitude-shift keying (ASK) is a type of amplitude modulation that represents digital data as difference in the amplitude of the carrier signal. In an ASK modulating system, the binary data 1 is symbolized by transmitting a fixed-amplitude carrier wave and fixed frequency for a bit duration of T units. If the signal value is 1 then the carrier signal will be transmitted; otherwise, nothing will be transmitted. Frequency and phase are kept unchanged during signal transmission.

A finite number of amplitudes is used by ASK modulation, each bit encode different amplitude pattern. The demodulator uses symbol-set which is designed by the modulator and determines the amplitude of the received signal and maps it back to the symbol it exhibits, thus recovering the original data.

II.IV. UART (RS232) ProtocolUniversal Asynchronous Receiver/Transmitter or UART in short used for the serial communication via the serial port. The transmitting UART converts parallel data to serial form, transmits data in serial to the receiving UART, then receiving UART converts the serial data back into parallel form for the receiving device or system.

UART is asynchronouslyprotocol that means is no clock signal to synchronize. However, both transmitter and receiver part must be worked with same clock speed. The transmitting part transferred the data packets with adding start and stop bits. Thanks to these bits, receiver part understands when its start to read bits and when its finish reading. If a start bit detected from receiver part, it starts to read coming data bits at a particular frequency known as the baud rate. Measure of the speed of data expressed with baud rate in bits per second. As previously said, both part must work at the same baud rate.

Generally, in UART protocol data is taken from CPU or necessary module in parallel form. The transmitter part convert parallel data to serial and it adds start, stop and parity bit when creating data packet. Next, the data packet is sent serially, bit by bit at the Tx pin. The data packet is read by receiver part from the Rx pin, one data bit at a time. After that, receiver part removes the start, stop and parity bit in data and convert it serial to parallel, and transmission is end.

In our project, data is taken from BROM in parallel form. The transmitter part convert parallel data to serial and it adds start and stop bit creating data packet. Next, the data packet is sent serially, bit by bit at the TxD pin. The data packet is read by receiver part from RxD pin, one data bit at a time. After that, receiver part removes the start and stop bit in data and convert it serial to parallel and store them in BRAM.

In project, communication part so similar with UART protocol. However, in our Project start and stop bit is not inserted every data packet. We sent start bit at the beginning of transmission and stop bit at the end of the transmission.

II.V. HOW TO UPLOAD IMAGE TO A BLOCK ROMWith the Matlab code, image pixel information saved in a file with a code extension. The core file extension is related to specialized applications and development environments created by the Xilinx, Inc., like ISE Design Suite etc. The code file includes BRAM (Block RAM) or BROM (Block ROM) initialization code. In the same code, the data size of the image is reduced eight to three, image is eliminated from redundant bits. Process of reducing data size eight to three means color average is decreased. In other words, the image which will be used should contain primary colors. Primary color is red, green, blue. For this reason, at first trial of project made with image that is created on paint contain only RGB colors.

Once the code file has been created, this file open with Notepad ++..coe file contains pixel information of image, therefore when its open, it will be copied and pasted in BROM.

III. Design

Ozden ERDINC & Emine Zeynep OZDONER

Alex Wong

Alex Wong

Comments