Introduction: Why Build a Processor? We use computers every day, but for many of us, the CPU remains a "black box." Magic happens inside, and results come out. As an Electronics & Communication Engineering student, I wanted to break that black box open.

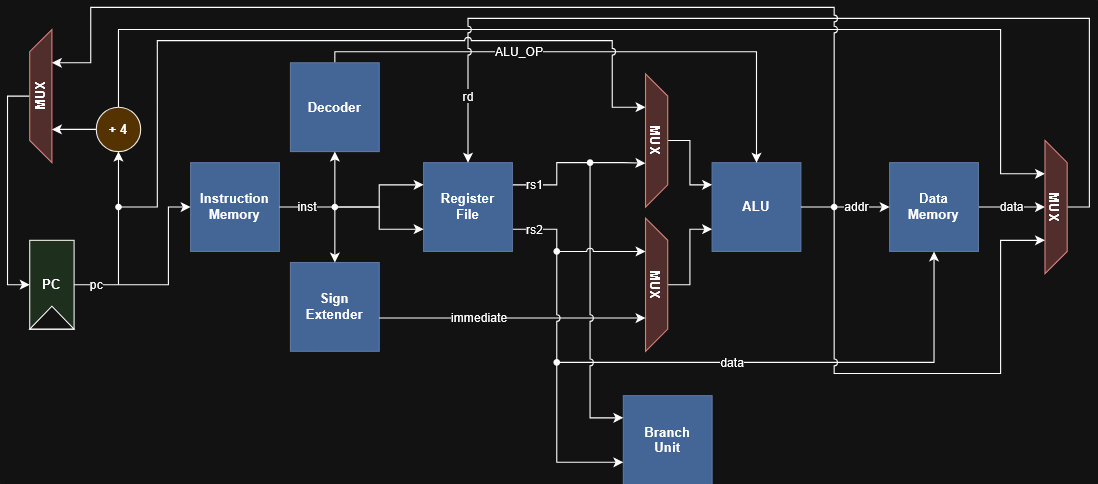

I decided to build a 32-bit Single-Cycle Processor based on the open-source RISC-V ISA (Instruction Set Architecture). Unlike proprietary architectures like x86 or ARM, RISC-V is open, clean, and perfect for learning how silicon logic actually works.

In this project, I will walk you through designing the datapath, implementing the control logic, and simulating your own CPU core using entirely free and open-source tools.

What You Will Learn:How a CPU fetches and executes instructions.

- How a CPU fetches and executes instructions.

Designing digital logic modules (ALU, Register File) in Verilog.

- Designing digital logic modules (ALU, Register File) in Verilog.

Verifying hardware designs using Icarus Verilog and GTKWave.

- Verifying hardware designs using Icarus Verilog and GTKWave.

The Architecture:This project implements the RV32I Base Integer Instruction Set. It features a Harvard Architecture style datapath (separate paths for instruction and data) and executes instructions in a single clock cycle. We will implement support for:

Arithmetic: ADD, SUB, ADDI

Logical: AND, OR, XOR

Control Flow: Branch preparation logic

Comments